Артикул: 1168674

Раздел:Технические дисциплины (112171 шт.) >Электроника (в т.ч. микроэлектроника и схемотехника) (4463 шт.) >

Схемотехника (958 шт.)

Название или условие:

Лабораторная работа №4. Исследование комбинационных логических устройств.

5.3. Ход работы. Уровень B.

Вариант 11

Описание:

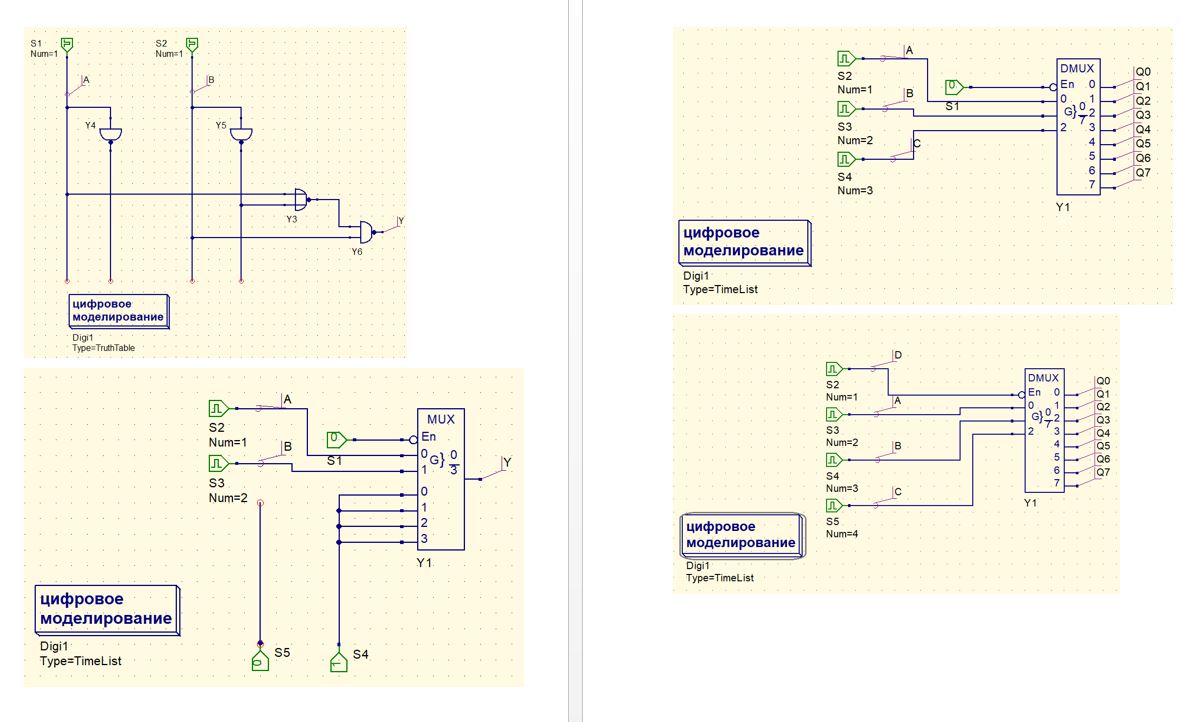

Исследование логических элементов

1. Запустите QUCS. Все необходимые компоненты содержатся в разделе Цифровые компоненты. Начните собирать схему с цифровых источников, расположите их вертикально, выводами вниз. Это будут входы a и b нашей схемы. От каждого источника проведите проводник вертикально вниз на такое расстояние, чтобы оно перекрывало все элементы логических операций по высоте (их длину потом можно изменить). Дважды кликните, чтобы обрезать проводник в нужном месте.

2. Добавьте на схему к каждому источнику инвертированный сигнал, как показано на рисунке. Добавьте метки проводника.

3. Соберите нижнюю часть схемы, согласно вашему варианту из таблицы 1. Добавьте на выходе метку проводника Y.

4. Добавьте Цифровое моделирование и смените в его настройках тип модели на Verilog.

5. Запустите моделирование, вернитесь на схему. Добавьте таблицу истинности, выберите двойным щелчком метки проводника a,b и Y. Перепишите ее и приложите к отчету.

Исследование мультиплексора.

1. Создайте новый файл схемы в QUCS.

2. Соберите схему на рисунке. Добавьте метки проводника, обозначить их согласно схеме. Подключите входы 0-3 к логическому нулю и единице в той же последовательности, что и значения Y из таблицы истинности, полученной при изучении логических функций.

3. У мультиплексора установите задержку на выходе, равную 0.

4. Настроить цифровые источники. Для первого установить времена переключения 1 мс и 1 мс, у второго 2 мс и 2 мс.

5. Добавить вид моделирования: «Цифровое моделирования».

6. Настроить цифровое моделирование: тип – TimeList, продолжительность моделирования – 8 мс, модель – Verilog.

7. Сохранить схему.

8. Запустить моделирование. Вернуться на схему.

9. Добавить временную диаграмму, выбрать двойным щелчком напряжение на метках проводника.

10. Сделать скриншот схемы и диаграммы, приложить их к отчету.

11. Проанализировать диаграммы и составить таблицу истинности изученного мультиплексора. Сравнить ее с таблицей истинности, полученной при изучении логических функций. Сделать выводы.

Исследование демультиплексора в режиме дешифратора

1. Создайте новый файл схемы в QUCS.

2. Соберите схему на рисунке. Добавьте метки проводника, обозначьте их согласно схеме.

3. У демультиплексора установить задержку на выходе равную 0.

4. Настроить цифровые источники:

5. Добавить вид моделирования: «Цифровое моделирования».

6. Настроить цифровое моделирование: тип – TimeList, продолжительность моделирования – 8 мс, модель – Verilog.

7. Сохранить схему.

8. Запустить моделирование. Вернуться на схему.

9. Добавить временную диаграмму, выбрать двойным щелчком напряжение на метках проводника. Рекомендуется следующий порядок: C, B, A, Q7, Q6, Q5, Q4, Q3, Q2, Q1, Q0.

10. Сделать скриншот схемы и диаграммы, приложить их к отчету.

11. Проанализировать диаграммы и составить таблицу истинности изученного дешифратора. Сделать выводы.

Исследование демультиплексора

1. Создайте новый файл схемы в QUCS.

2. Соберите схему на рисунке. Добавьте метки проводника, обозначьте их согласно схеме.

3. У демультиплексора установить задержку на выходе равную 0.

4. Настроить цифровые источники:

5. Добавить вид моделирования: «Цифровое моделирования».

6. Настроить цифровое моделирование: тип – TimeList, продолжительность моделирования – 16 мс, модель – Verilog.

7. Сохранить схему.

8. Запустить моделирование. Вернуться на схему.

9. Добавить временную диаграмму, выбрать двойным щелчком напряжение на метках проводника. Рекомендуется следующий порядок: C, B, A, D, Q7, Q6, Q5, Q4, Q3, Q2, Q1, Q0.

10. Сделать скриншот схемы и диаграммы, приложить их к отчету.

11. Проанализировать диаграммы и составить таблицу истинности изученного дешифратора. Сделать выводы.

Подробное решение в WORD+файлы QUCS для каждого раздела (12 файлов)

Изображение предварительного просмотра:

Процесс покупки очень прост и состоит всего из пары действий:

1. После нажатия кнопки «Купить» вы перейдете на сайт платежной системы, где можете выбрать наиболее удобный для вас способ оплаты (банковские карты, электронные деньги, с баланса мобильного телефона, через банкоматы, терминалы, в салонах сотовой связи и множество других способов)

2. После успешной оплаты нажмите ссылку «Вернуться в магазин» и вы снова окажетесь на странице описания задачи, где вместо зеленой кнопки «Купить» будет синяя кнопка «Скачать»

3. Если вы оплатили, но по каким-то причинам не смогли скачать заказ (например, случайно закрылось окно), то просто сообщите нам на почту или в чате артикул задачи, способ и время оплаты и мы отправим вам файл. Условия доставки: Получение файла осуществляется самостоятельно по ссылке, которая генерируется после оплаты. В случае технических сбоев или ошибок можно обратиться к администраторам в чате или на электронную почту и файл будет вам отправлен. Условия отказа от заказа: Отказаться возможно в случае несоответсвия полученного файла его описанию на странице заказа. Возврат денежных средств осуществляется администраторами сайта по заявке в чате или на электронной почте в течении суток.