Артикул: 1165619

Раздел:Технические дисциплины (109117 шт.) >Электроника (в т.ч. микроэлектроника и схемотехника) (4232 шт.) >

Схемотехника (890 шт.)

Название или условие:

Курсовая работа по дисциплине: «Цифровая микроэлектроника»

на тему: «МАЖОРИТАРНАЯ СХЕМА 3 ИЗ 5 С УПРАВЛЕНИЕМ»

Используя интегральные схемы серии 1533 спроектировать мажоритарную схему 3 из 5 с управлением:

В зависимости от комбинации на управляющих входах на выход должен проходить сигнал с одного из 5 информационных входов, либо мажорированный сигнал. Выполнение задания осуществляется 2 способами: проектирование наименьше схемы в логическом базисе 2И-НЕ, т.е. такой схемы, в которой будет наименьшее число логических элементов базиса; и проектирование схемы с минимальным числом элементов серии, т.е. схемы с наименьшим числом микросхем.

Для каждого из способов привести:

1. Функциональную схему или УГО;

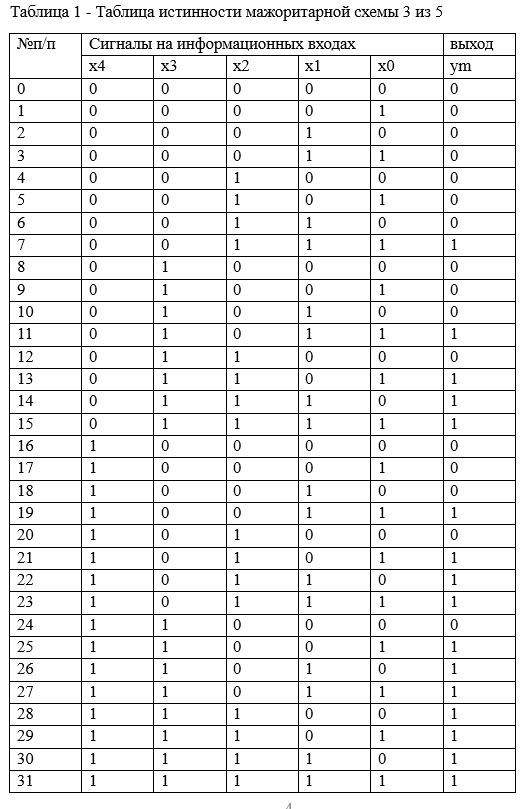

2. Таблицу истинности;

3. Решение задачи оптимизации (карты Карно или аналитические зависимости);

4. Две принципиальные схемы, временные диаграммы, смоделированные в САПР «Quartus II»;

5. Две принципиальные электрические схемы по ЕСКД;

6. Перечни элементов;

7. Схему размещения элементов на печатной плате.

Описание:

Задание курсовой работы 3

Ход работы 4

Мажоритарная схема 3 из 5 4

Дешифратор 7

Реализация схемы минимальным числом элементов серии 11

Вывод 16

Изображение предварительного просмотра:

Процесс покупки очень прост и состоит всего из пары действий:

1. После нажатия кнопки «Купить» вы перейдете на сайт платежной системы, где можете выбрать наиболее удобный для вас способ оплаты (банковские карты, электронные деньги, с баланса мобильного телефона, через банкоматы, терминалы, в салонах сотовой связи и множество других способов)

2. После успешной оплаты нажмите ссылку «Вернуться в магазин» и вы снова окажетесь на странице описания задачи, где вместо зеленой кнопки «Купить» будет синяя кнопка «Скачать»

3. Если вы оплатили, но по каким-то причинам не смогли скачать заказ (например, случайно закрылось окно), то просто сообщите нам на почту или в чате артикул задачи, способ и время оплаты и мы отправим вам файл. Условия доставки: Получение файла осуществляется самостоятельно по ссылке, которая генерируется после оплаты. В случае технических сбоев или ошибок можно обратиться к администраторам в чате или на электронную почту и файл будет вам отправлен. Условия отказа от заказа: Отказаться возможно в случае несоответсвия полученного файла его описанию на странице заказа. Возврат денежных средств осуществляется администраторами сайта по заявке в чате или на электронной почте в течении суток.