Артикул: 1165061

Раздел:Технические дисциплины (108563 шт.) >Электроника (в т.ч. микроэлектроника и схемотехника) (4149 шт.) >

Схемотехника (866 шт.)

Название или условие:

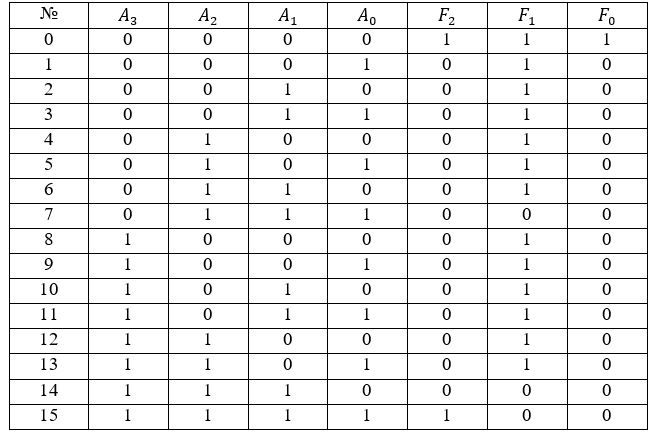

Система управления и блокировки (СУБ) содержит четыре датчика (А0, А1, А2, А3) и три сигнальных элемента (F0, F1, F2). Сигнальный элемент F0 дает команду на включение исполнительного элемента (ВИЭ), сигнальный элемент F1 («Внимание») приводит в состояние «Готовность к включению» систему аварийной блокировки, сигнальный элемент F2 («Авария») включает систему аварийной блокировки. В условии ДЗ приводится логика работы СУБ (А0, А1, А2, А3 – входы, F0, F1, F2 - выходы).

Требуется:

1. Составить таблицу истинности (см. Примечание).

2. Записать Булеву функцию, используя СДНФ или СКНФ.

3. Минимизировать функцию, используя карты Карно или правила Булевой арифметики.

4. Составить схему, реализующую Булеву функцию, при этом обеспечить следующие временные приоритеты:

- сигнал «Авария» (F2) не может опережать сигнал «Внимание» (F1);

- сигнал «Авария» (F2) должен опережать сигнал «ВИЭ» (F0).

5. Оптимизировать схему, обеспечив минимальное количество корпусов микросхем и минимальное количество номиналов микросхем, сохраняя при этом временные приоритеты.

6. Выбрать из справочной литературы типы микросхем, составить принципиальную электрическую схему устройства. Справочные данные микросхем оформить в виде таблицы приложения.

7. Рассчитать время задержки включения исполнительного элемента и время задержки срабатывания системы аварийной блокировки.

8. Сделать выводы.

Вариант 4a

Описание:

Примечание:

Для вариантов «а», «б», «в», «г» в таблице истинности сделать изменения в соответствии со следующими условиями:

- для вариантов «а» активным для выходов F0 и F1 является низкий логический уровень, для выхода F2 - высокий.

- для вариантов «б» активным для выходов F1 и F2 является низкий логический уровень, для выхода F0 - высокий.

- для вариантов «в» активным для выходов F0 и F2 является низкий логический уровень, для выхода F1 - высокий.

- для вариантов «г» активным для выходов F0, F1 и F2 является низкий логический уровень.

Вариант 4a

Включение исполнительного элемента происходит при срабатывании одного из датчиков. Сигнал «Внимание» активизируется при срабатывании трех смежных датчиков. Аварийным является режим отсутствия срабатывания датчиков или срабатывание четырех датчиков одновременно.

Активным для выходов F0 и F1 является низкий логический уровень, для выхода F2 - высокий.

Подробное решение WORD

Изображение предварительного просмотра:

Процесс покупки очень прост и состоит всего из пары действий:

1. После нажатия кнопки «Купить» вы перейдете на сайт платежной системы, где можете выбрать наиболее удобный для вас способ оплаты (банковские карты, электронные деньги, с баланса мобильного телефона, через банкоматы, терминалы, в салонах сотовой связи и множество других способов)

2. После успешной оплаты нажмите ссылку «Вернуться в магазин» и вы снова окажетесь на странице описания задачи, где вместо зеленой кнопки «Купить» будет синяя кнопка «Скачать»

3. Если вы оплатили, но по каким-то причинам не смогли скачать заказ (например, случайно закрылось окно), то просто сообщите нам на почту или в чате артикул задачи, способ и время оплаты и мы отправим вам файл. Условия доставки: Получение файла осуществляется самостоятельно по ссылке, которая генерируется после оплаты. В случае технических сбоев или ошибок можно обратиться к администраторам в чате или на электронную почту и файл будет вам отправлен. Условия отказа от заказа: Отказаться возможно в случае несоответсвия полученного файла его описанию на странице заказа. Возврат денежных средств осуществляется администраторами сайта по заявке в чате или на электронной почте в течении суток.